Product Summary

The M11B416256A-35TG is a randomly accessed solid state memory, organized as 262,144 x 16 bits device. It offers Extended Data-Output , 5V( ± 10%) single power supply. Access time (-25,-28,-30,-35,-40) and package type (SOJ, TSOP II) are optional features of this family. The M11B416256A-35TG has CAS - before -RAS ,RAS -only refresh and Hidden refresh capabilities. Two access modes are supported by the M11B416256A-35TG: Byte access and Word access. Use only one of the two CAS and leave the other staying high will result in a BYTE access. WORD access happens when two CAS ( CASL , CASH) are used. CASL transiting low during READ or WRITE cycle will output or input data into the lower byte (IO0~IO7), and CASH transiting low will output or input data into the upper byte (IO8~15).

Parametrics

M11B416256A-35TG absolute maximum ratings: (1)Voltage on Any pin Relative to Vss: -1V to +7V; (2)Operating Temperature, TA (ambient): 0 ℃ to +70 ℃; (3)Storage Temperature (plastic): -55 ℃ to +150 ℃; (4)Power Dissipation: 1.43W; (5)Short Circuit Output Current: 50mA.

Features

M11B416256A-35TG features: (1)X16 organization; (2)EDO (Extended Data-Output) access mode; (3)2 CAS Byte/Word Read/Write operation; (4)Single 5V ( ± 10%) power supply; (5)TTL-compatible inputs and outputs; (6)512-cycle refresh in 8ms; (7)Refresh modes :RAS only, CAS BEFORE RAS (CBR) and HIDDEN; (8)JEDEC standard pinout; (9)Key AC Parameter.

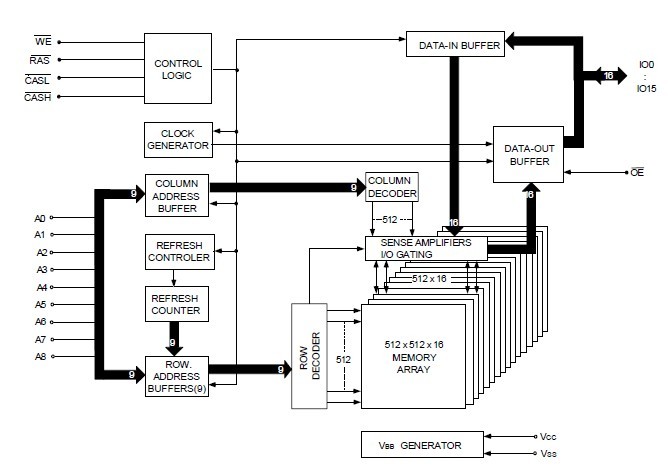

Diagrams

|

M11B11664A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

M11B416256A |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))